计算机存储系统核心机制 双口RAM、Cache映射、替换算法与写策略

在计算机组成原理的存储系统体系中,除了主存与辅存的基本结构外,还涉及一系列提升性能与保证数据一致性的关键技术。本文将在“存储系统 下”的框架内,系统性地探讨双口RAM的工作原理、Cache的地址映射方式、常见的替换算法以及Cache的写策略,并简要阐述其在计算机系统集成中的意义。

一、 双口RAM:并行访问的存储解决方案

双口RAM是一种具有两套独立地址线、数据线和控制线的静态随机存储器。其核心优势在于允许两个端口同时、独立地对存储阵列进行读写操作(只要不是同时访问同一个存储单元),从而有效解决了多处理器系统或高速外设与CPU之间的数据共享与通信瓶颈。在系统集成中,双口RAM常被用作高速数据缓冲区或共享内存,是实现模块间高效、实时数据交换的关键器件。

二、 Cache的地址映射方式

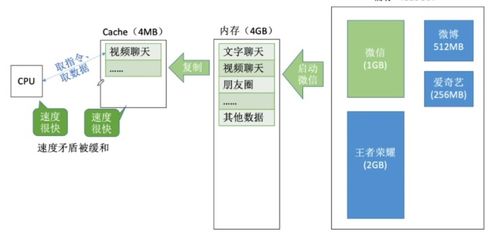

Cache是介于CPU与主存之间的小容量高速存储器,其有效性的基础在于良好的地址映射策略,即确定主存块与Cache行之间的对应关系。主要有三种方式:

- 直接映射:每个主存块只能映射到Cache中一个固定的行。规则简单,硬件实现成本低,但冲突不命中率高,Cache利用率可能不佳。

- 全相联映射:每个主存块可以映射到Cache中的任意一行。空间利用率最高,冲突不命中率低,但查找时需要比较所有行的标记,电路复杂、速度慢、成本高。

- 组相联映射:前两种方式的折中。将Cache行分组,主存块映射到特定组内的任意一行。它有效平衡了命中率与硬件复杂度,是实践中最常用的映射方式(如2路、4路、8路组相联)。

三、 Cache替换算法

当新数据需要调入Cache而对应位置已被占用时,需要根据特定算法选择一行进行替换。常见算法有:

- 随机替换(RAND):随机选择一行替换。实现简单,但未考虑程序访问的局部性,命中率不稳定。

- 先进先出(FIFO):替换最早调入Cache的行。实现容易,但可能淘汰掉经常被访问的“老”数据。

- 最近最少使用(LRU):替换最近一段时间内最久未被访问的行。能较好地反映程序局部性,命中率高,是理论上最优的算法之一,但硬件实现相对复杂(需要记录访问历史)。

- 最不经常使用(LFU):替换访问次数最少的行。需要为每行维护一个计数器,实现开销较大,且可能“粘住”早期频繁访问但后续不再使用的数据。

四、 Cache写策略

当CPU执行写操作命中Cache时,需要解决Cache数据与主存数据的同步问题,主要策略有:

- 写直达:同时写入Cache和主存。能始终保持主存数据是最新的,简化了一致性管理,但每次写操作都要访问慢速主存,总线 traffic 大,降低了系统效率。

- 写回:只写入Cache,并将该行标记为“脏”。仅当该脏行被替换时,才将其写回主存。减少了访存次数,提高了效率,但存在数据不一致的窗口期,需要额外的“脏位”来标识状态。

当写操作未命中Cache时,通常有两种处理方式:

- 写分配:先将主存对应块调入Cache,然后在Cache中完成写操作(通常与“写回”策略配合使用)。

- 非写分配:直接写入主存,而不将数据块调入Cache(通常与“写直达”策略配合使用)。

五、 计算机系统集成视角

在计算机系统集成中,上述技术并非孤立存在,而是协同工作,共同构建高效、可靠的存储层次结构。设计者需要根据系统的性能目标(速度)、成本约束和一致性要求进行权衡选择。例如,在高性能多核处理器中,可能采用多级Cache结构(L1, L2, L3),其中L1 Cache常采用写直达与写分配以保证核心内速度与简化一致性协议,而末级共享L3 Cache则可能采用写回与非写分配以减少片外内存访问。双口RAM或更复杂的多端口存储器可能被集成在芯片内部或作为外围接口缓存,以协调CPU、DMA控制器、图形处理器等不同主设备之间的数据流。

深入理解双口RAM、Cache映射、替换算法与写策略的原理与优劣,是进行高性能计算机存储子系统设计与系统集成的基石。这些技术的巧妙结合与应用,直接决定了计算机系统处理数据的速度与效率。

如若转载,请注明出处:http://www.jiadenakeji.com/product/26.html

更新时间:2026-04-12 18:30:52